📑 목차

SoC·칩렛을 넘어, 시스템 전체가 하나의 거대한 연산 생태계가 되는 미래

여러 연산 기관이 분산되어 있으면서도 서로 깊이 연결된 새로운 컴퓨팅 구조

핵심요약

2025년 현재, 컴퓨팅 구조는 CPU 중심을 넘어 여러 종류의 연산 장기가 협력하는 시대로 이동하고 있다.

칩셋·SoC·CXL·UCIe 같은 기술은 이제 연구 수준이 아니라 현실적인 산업 로드맵에 확고하게 자리 잡았다.

CXL은 실제 서버 시장에서 상용화가 시작되었고, NVLink·InfiniBand는 이미 AI 산업의 표준이다.

UCIe는 아직 초기 생태계 조성 단계이지만, 반도체 업계 전체가 참여 중이라 향후 칩셋 호환의 핵심 규격이 될 가능성이 크다.

미래에는 단일 장비가 아니라 연결된 장비 전체가 하나의 두뇌처럼 작동하는 “분산 지능 구조”로 확장될 것이다.

1. 개념 설명 - “컴퓨터 한 대를 넘어서, 전체가 하나의 두뇌가 된다”

핵심 문장: 미래의 컴퓨팅은 ‘한 곳에 모인 연산’이 아니라 ‘여러 곳에 흩어져 있으면서도 하나처럼 움직이는 연산’이다.

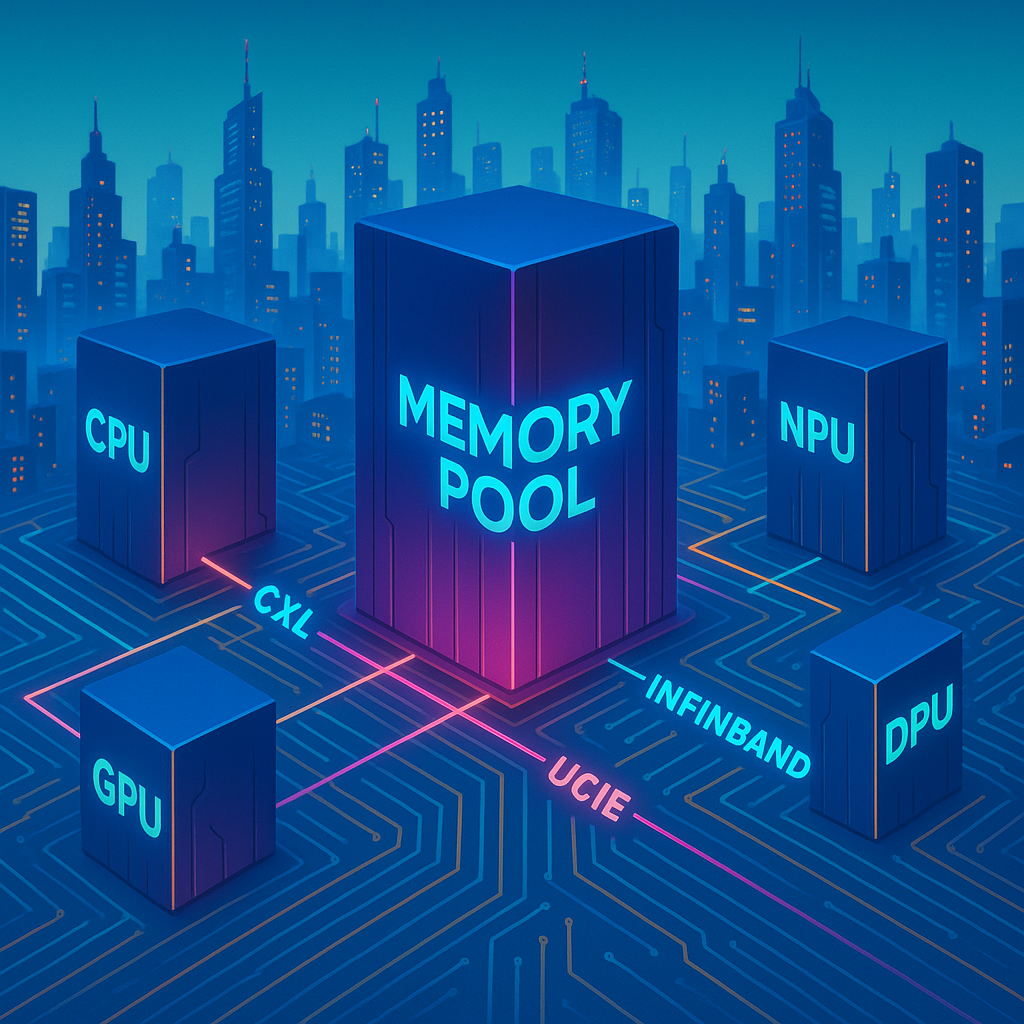

과거의 컴퓨터는 CPU가 중심으로 연산을 수행하고 메모리·GPU·스토리지 같은 나머지 장치는 주변 요소로 기능했다. 그러나 2020년대 이후 CPU·GPU·NPU·DPU·FPGA 등 각기 다른 특성을 가진 연산 장기들이 등장하고 구체화되면서 시스템은 더 이상 “중심이 존재하는 피라미드 구조”가 아니라 “여러 두뇌가 협력하는 네트워크 구조”로 진화하고 있다. 그리고 이 연산 장기들은 같은 칩 안에 있을 수도 있지만, 서로 다른 장치나 심지어 다른 서버에 있어도 고속 링크로 연결되면 하나의 거대한 연산 엔진처럼 움직일 수 있다.

2. 분산형 두뇌 구조의 핵심 - “CXL과 UCIe가 만든 새로운 연결 방식”

미래 컴퓨팅을 정의하는 핵심은 인터커넥트다. 이 기술은 단순한 연결선을 뛰어넘어 “하드웨어의 신경망” 역할을 한다.

2-1. CXL(Compute Express Link) - 공유 메모리 시대의 시작

2025년 현재 CXL 2.0/3.0은 이미 서버·데이터센터 시장에서 상용화가 시작된 상태다. 아직 범용 PC까지 내려오진 않았지만, 클라우드와 AI·HPC 서버에서는 실험·채택이 빠르게 확산 중이다.

CXL이 열어주는 핵심 변화:

- CPU·GPU·DPU가 서로의 메모리에 복사 없이 접근

- 메모리를 “DIMM으로 확장”하는 것이 아니라 “메모리 서버로 확장”

- 수십 TB 단위의 대규모 메모리 풀 구성

- AI 모델 학습 시 메모리 병목을 대폭 해소

CXL은 여러 연산 장기가 동시에 열람하는 하드웨어급 공유 드라이브다.

2-2. UCIe(Universal Chiplet Interconnect Express) - 칩셋의 범용 언어

UCIe는 2022년 발표 이후 인텔·AMD·삼성·TSMC·구글·ARM 등 주요 기업이 참여하는 칩렛 통신 표준이다.

2025년 기준 현황은 이렇다:

- 아직 본격적 대량 상용 제품은 많지 않음

- 그러나 칩 제조사들이 개발 플랫폼·노드·도구를 빠르게 정비 중

- 서로 다른 회사가 만든 칩셋도 하나의 패키지로 조립할 수 있는 기반이 됨

미래에는

- NVIDIA GPU 칩렛 + 삼성 메모리 칩렛 + Intel I/O 칩렛 같은 조합도 기술적으로 가능해진다.

UCIe는 반도체 업계의 USB다. 누가 만들든 연결 규칙이 통일되는 구조.

2-3. NVLink·InfiniBand·Infinity Fabric - 이미 현실이 된 초연결 구조

- NVLink → GPU ↔ GPU 간 초고속 연결

- InfiniBand → 서버 ↔ 서버 간 저지연 네트워크

- Infinity Fabric → AMD 칩렛 간 통신 규격

이들 기술은 미래 기술이 아니라 이미 현재 AI 산업의 기본 인프라다. GPT·Llama 등 대규모 AI 모델은 이 고속 연결 없이는 학습 자체가 불가능하다. 즉, 초연결 시스템은 이미 현실이다.

3. 메모리·스토리지·가속기의 경계가 사라지는 중

2025년 현재, 메모리와 스토리지의 역할은 빠르게 섞이고 있다.

SSD를 RAM처럼 활용하는 기술

- NVMe over Fabrics (NVMe-oF)

- ZNS(Zone Namespace) 구조

초고속 NVMe SSD가 대규모 메모리 풀 확장에 참여하고 있다.

RAM의 외부 확장화

- Memory Pooling

- Memory Tiering

- CXL 기반 메모리 서버

서버 여러 대의 메모리가 “하나의 논리적 메모리”처럼 보이기도 한다.

가속기 중심 구조로의 전환

AI·HPC·로보틱스 분야에서는 CPU가 연산 중심이 아니라 스케줄러 역할로 바뀌고 있다. 실제 연산은 대부분 GPU·NPU·DPU가 담당한다. 미래의 메모리 구조는 “하나의 큰 저장고”가 아니라 여러 강줄기가 모여 하나의 거대한 삼각주를 이루는 구조다.

4. 비유하자면 - “전두엽 하나가 아니라, 서로 연결된 여러 뇌 영역의 협업”

미래 컴퓨팅 구조는 신경과학과 매우 닮아간다.

- CPU → 전두엽 (논리·제어)

- GPU → 시각 피질 (패턴·병렬 처리)

- NPU → 소뇌·언어 영역 (추론·학습)

- DPU → 신경 배선(시냅스) 관리

- 메모리·스토리지 → 해마

- 인터커넥트 → 시냅스 네트워크

즉, 미래 시스템은 단일 두뇌 구조가 아니라 ‘다중 두뇌 시스템’이다.

5. 기술 발전 과정 - “단일 → 병렬 → 통합 → 초연결 → 분산 지능”

컴퓨팅 진화는 다음 흐름을 따라왔다.

- 싱글코어 CPU 시대

- 멀티코어 CPU 시대

- GPU 중심의 병렬 컴퓨팅 부상

- SoC 통합 구조 확대

- 칩렛 구조 상용화 (AMD·Intel)

- CXL/UCIe 기반의 확장형·모듈형 시스템

- 여러 장비가 하나의 연산 구조를 이루는 ‘분산형 지능 시스템’

2025년 기준, 1~6단계는 이미 산업계에서 실현되었고, 7단계가 지금 막 시작되는 과도기라고 볼 수 있다.

6. 오늘날 활용 예시 - 일정 부분은 이미 현실, 일정 부분은 전환 중

AI 모델 학습 시스템

- NVLink·InfiniBand 기반의 초연결 GPU 클러스터

- 메모리 서버 + 스토리지 노드 + GPU 노드가 하나의 거대한 연산 엔진처럼 작동

클라우드 데이터센터

- CPU 서버가 아니라 “가속기·메모리·스토리지를 조합하는 방식”으로 확장

- CXL 기반 메모리 풀 실험·선도 적용 시작

엣지 컴퓨팅

- 카메라·센서·AI·통신·보안 처리 기능이 하나의 SoC 내부에서 통합

- 목적형 연산 장기가 실시간 협력

자동차 ADAS

- CPU·GPU·NPU·ISP·센서 허브가 초저지연 링크로 묶임

- 인간의 감각-판단-반응 체계를 모방한 구조

7. 요약

- 미래의 컴퓨팅은 “한 장비 안의 구조”가 아니라 장비 간을 포함한 전체 연결 구조로 완성된다.

- NVLink·InfiniBand는 이미 현실이며, CXL은 상용화가 시작된 단계, UCIe는 생태계가 형성 중이다.

- 여러 연산 장기가 서로의 강점을 결합하는 분산 지능 시대가 도래하고 있다.

- 컴퓨팅의 본질은 “부품 조립”에서 “지능 모듈 설계”로 이동 중이다.

8. 다음 편 예고

이제 시리즈 마지막에서는 CPU → 메모리 → 저장장치 → 전원 → GPU → 통합 구조 → 미래 구조까지 전편의 흐름을 하나로 묶어 컴퓨터라는 거대한 생명체의 전체 구조를 총정리한다.

'컴퓨터 과학 > 통합구조' 카테고리의 다른 글

| [하드웨어 뜯어보기] 시리즈 대단원 - 컴퓨터라는 거대한 생명체의 전체 구조 (0) | 2025.12.01 |

|---|---|

| [하드웨어 뜯어보기] 통합 구조 #45 - 미래의 시스템 구조 (0) | 2025.12.01 |

| [하드웨어 뜯어보기] 통합 구조 #44 – 하드웨어 통합 구조 (0) | 2025.11.28 |